程序員必知的 CPU 中斷機制:提升系統性能的關鍵技術

在現代計算機系統中,CPU作為核心處理單元,需要與各種硬件設備進行高效協調工作。從鍵盤輸入到網絡數據傳輸,從磁盤讀寫到圖形渲染,CPU必須能夠及時響應各種硬件設備的請求,同時又不能因為等待這些相對較慢的設備而降低整體系統性能。這就引出了計算機系統中至關重要的機制——中斷處理。

中斷機制使得CPU可以在執行當前任務的同時,及時響應來自各種硬件設備的緊急請求。隨著計算機技術的發展,從單核到多核,從簡單設備到復雜外設,中斷處理機制也在不斷演進和優化。本文將深入探討CPU與硬件設備交互的演進歷程,從最早的中斷控制器到現代APIC架構,以及如何通過CPU親和力等技術優化多核系統的性能。

一、詳解CPU與其他硬件交互的演進

1. 中斷控制器

計算機發展初期,CPU除了執行必要的指令以外,還需要和鍵盤、網卡、鼠標、硬盤等各種設備進行交互。鑒于這些設備執行速度與CPU不對等,為了避免CPU為了響應這些中斷而進行等待,便提出了中斷響應機制。實現方式也很簡單,所有硬件設備都和中斷控制器綁定,當其他事件需要CPU調度執行時,通過中斷驅動程序發送信號,CPU在完成手頭的指令后都會查看中斷信號,若看到信號則直接響應中斷:

因為響應中斷時需要暫時放下手里正在執行的指令,所以為了能夠在完成響應后繼續執行線程的后續工作,CPU在響應中斷前會將線程在各個寄存器中的數值保存到線程棧中,等待完成中斷響應后取出恢復現場繼續工作。

在特定情況下CPU不會響應可屏蔽中斷,即當EFLAGS寄存器中的IF標志位為0時(正在執行優先級較高的事件或處于中斷禁用狀態)。但是一旦遇到NMI(Non-Maskable Interrupt)中斷,這意味著系統發生致命錯誤或者硬件異常(如筆記本溫度過高、電源斷電)等異常情況,NMI中斷是不可屏蔽的,CPU必須響應。

2. 傳統中斷的缺陷和PIC的引入

隨著計算機的演進,需要交互的硬件設備越來越多,于是設計者們引入了一個芯片專門處理不同的硬件中斷控制——PIC(Programmable Interrupt Controller)即8259A芯片。PIC針對每個硬件都進行編號,也就是中斷向量,同時針對每個硬件中斷都配備對應的中斷處理函數,最后將中斷向量和處理函數地址進行映射,構建出一張IDT(Interrupt Descriptor Table)表存放于內存中(CPU緩存空間有限),并通過IDTR(Interrupt Descriptor Table Register)指針進行管理:

因為IDT這一設計理念非常出色,所以設計者后續也將一些異常響應中斷(如除數為0、內存地址錯誤)及其處理函數也放到IDT表中。

3. APIC的優化

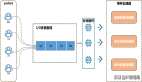

但隨著CPU核心數的增加,傳統的PIC對于中斷響應也表現得有些力不從心,于是整個架構演進為:

- 將PIC撤除

- 每個CPU內置一個APIC,對應名為Local APIC

- 外部配備一個I/O APIC

基于這個新架構,由I/O APIC處理外部硬件中斷請求并根據分發策略交給多核CPU中的某個Local APIC,讓Local APIC通知CPU處理中斷。 同時因為Local APIC的存在,各個CPU之間也能進行相互的中斷請求,這也就是IPI(Inter-Processor Interrupt),進一步提升了CPU之間各自通知中斷響應的效率:

4. 網卡中斷的性能瓶頸與CPU親和力的理念

互聯網發展后在并發網絡連接下,網卡單位時間內需要處理的網絡數據越來越多。按照原有的BSP(Bootstrap Processor)即第一個CPU處理網絡請求方案會導致CPU使用率偏斜,進而導致單核CPU過熱的情況,于是提出了負載均衡的設計理念。但是新的問題又來了,網絡消息一般都是來自特定的幾個網絡連接,每次CPU處理特定連接消息時就會將每個socket連接信息緩存下來,如果采用隨機負載均衡策略,就會出現當前連接此刻在當前CPU處理,下一刻又在別的CPU處理,多核CPU緩存大概率失效,每次處理消息都必須從相對低效的內存中加載數據,使得執行性能大大降低。

所以考慮到負載均衡且提升網絡消息包的處理效率,設計者們提出了CPU親和力的設計理念:

- 操作系統提供API,進程或中斷可以選擇是否需要保證CPU親和力

- 操作系統引入smp_affinity,使用者可以通過掩碼決定當前中斷綁定到哪個CPU

- APIC引入CPU親和寄存器,用于實現第二點的適配

由此網卡對應的連接消息既可以按照分發策略交給不同CPU響應中斷,并通過親和力寄存器保證和CPU綁定避免緩存失效,高效處理連接:

對應的我們也可以鍵入cat /proc/interrupts查看系統如何分配中斷給CPU,以MCP機器異常檢查輪訓來看,整體是負載均衡的:

CPU0 CPU1 CPU2 CPU3 CPU4 CPU5

......

NMI: 0 0 0 0 0 0 Non-maskable interrupts

LOC: 0 0 0 0 0 0 Local timer interrupts

SPU: 0 0 0 0 0 0 Spurious interrupts

PMI: 0 0 0 0 0 0 Performance monitoring interrupts

IWI: 1 0 0 0 0 0 IRQ work interrupts

RTR: 0 0 0 0 0 0 APIC ICR read retries

RES: 719671 736844 710157 718313 723883 724818 Rescheduling interrupts

CAL: 2770801 2519025 2333672 2228790 2230070 2189432 Function call interrupts

MCP: 1366 1366 1366 1366 1366 1366 Machine check polls

......二、小結

CPU與硬件設備的交互機制經歷了從簡單到復雜、從單核到多核的演進過程:

- 中斷機制的基礎:中斷機制是CPU與硬件設備交互的核心,通過中斷控制器協調CPU與各種設備的通信,避免CPU在等待設備響應時浪費計算資源。

- 從PIC到APIC的演進:隨著多核處理器的發展,傳統的PIC中斷控制器已無法滿足需求,APIC架構通過Local APIC和I/O APIC的分工合作,實現了更高效的中斷處理和CPU間通信。

- 性能優化策略:CPU親和力機制通過將特定中斷綁定到特定CPU核心,減少了緩存失效問題,提升了多核系統處理高并發網絡請求的性能。

- 現代中斷處理:現代系統還引入了MSI/MSI-X等更先進的中斷機制,提供了更靈活的中斷分發和處理能力。

理解這些機制有助于我們更好地進行系統調優和故障排查,特別是在處理高并發、低延遲的應用場景時。